今天想和我们谈谈计时器树综合性:Clock Tree Synthesis (CTS)。

构想了很久应该什么样如是说CTS,最终决定分为两篇该文来一步棋一步棋如是说整座业务流程。即使如此,由于在工程项目投资中CTS是一个比较复杂的组织工作,因而在本时评的该文之外可能将还有许多东西须要后端斯特默去重视。但我依然期望对新手,通过本时评接下去的两篇该文,能对CTS的基本业务流程和作法有位一大体的路子,从而防止领到一个design后陷于难上加难的消极。

嘿嘿,在P&R整座业务流程中,有两个对design的PPA(Power Performance Area)起关键性的关键步骤:Floorplan和CTS。即使如此,在前述工程项目中,许多人可能将组织工作数月也没机会做一次比较全面的CTS。另一方面其原因在于,P&R辅助工具尤其是FPS的ICC2和Innovus对相对简单的clock tree都能较好的处理;另另一方面的其原因是,对绝大多数无法碰触top的技师来说,block内部的clock结构大机率是非常简单的。因而就导致许多老师在做过几个工程项目前面对繁杂的clock依然难上加难。

特别针对这个现象,本时评期望根据自己的经验把CTS的核心思想的作法如是说给我们。如果我们之后碰到繁杂的clock时发现这儿的内容对前述组织工作多有助益,本时评也将告负自豪。

Clock Tree Synthesis,简而言之,就是对design的计时器树进行综合性。主要的目的是让每一clock都能在尽可能将短的时间内传达到它们驱动力的所有DFF(暂存器)。对CTS,我们有三个分项期望能尽可能将努力做到更快:

每一clock抵达其所驱动力的sink(DFF)的latency都尽可能将短;

每一clock内,以及有排程关系的clock之间的skew尽可能将小;

每一clock的common path尽可能将长。

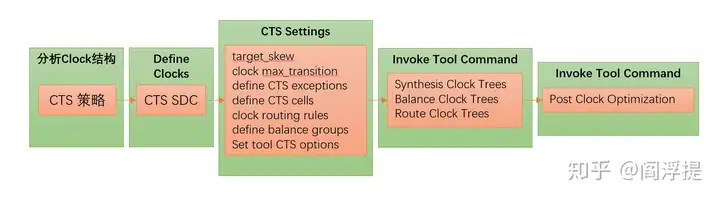

对绝大多数P&R辅助工具,CTS的flow可以归纳为以下形式:

CTS Flow须要指出的是,上图中可能将有些术语你还不太清楚具体涵义,但那些单厢在前面的如是说中逐一提到。我在这儿也没将大部分单字译成英语,因为期望我们读懂那些术语,这将使我们在之后阅读辅助工具的User Guide或者其他英语资料的时候能少许多心理障碍。

CTS策略

这是CTS的第一步棋,虽然在业务流程中只是简单的几个字,但特别针对繁杂的clock,这儿可能将须要花费大量的时间分析clock的结构,找出潜在可能将出现的问题和瓶颈,并特别针对我们上述提出的三个分项,决定如何去综合性计时器树。这一步棋如此重要却又非常容易被忽略,以至于有些老师在碰到繁杂的clock出现问题时无从分析,遑论如何改进。下面我将通过一个例子来说明,CTS策略到底是什么。(注:以下示例不对标任何前述设计,如有雷同,纯属巧合~)

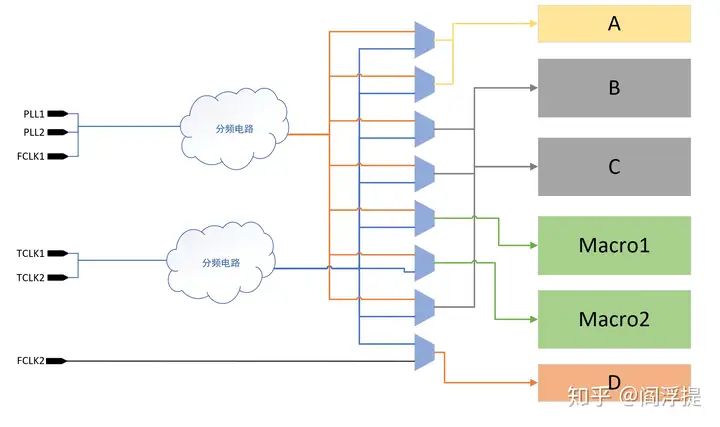

假设某芯片的clock结构可以简化成如下形式:

其中function clock从两个PLL和两个IO(FCLK1, FCLK2)进来,test clock从两个IO(TCLK1, TCLK2)进来。从图中可以看出,在分频电路之后,进入A和D的clock不与其他模块共享。

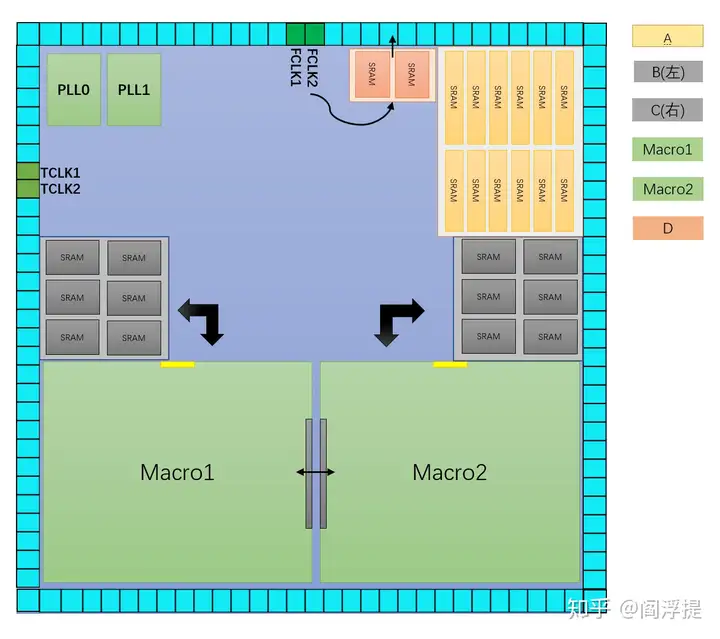

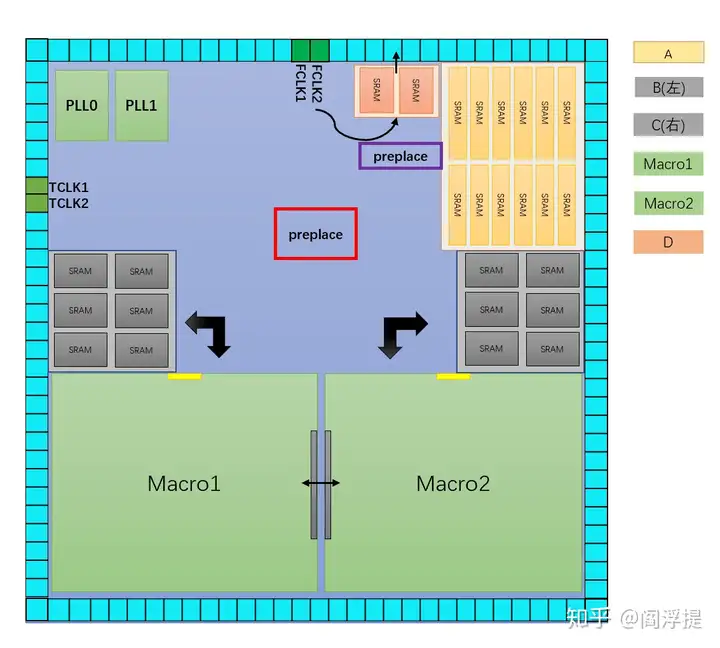

与此同时,我们假设芯片的floorplan可以表示为如下形式(注意clock source和模块位置与clock结构的对应关系):

如果模块之间的排程关系可以简述为如下形式:

Block B <-> Macro1

Block C <-> Macro2

Macro1 <-> Macro2

Block A/D为独立模块

考虑到上述计时器结构,floorplan和排程关系,我们该如何决定CTS策略呢?

在考虑策略之前,我们先回忆一下CTS的三个目标:latency尽可能将短;skew尽可能将小;common path尽可能将长。

先从最简单的开始:鉴于Block A和D为独立模块,它们不与其他模块产生排程关系,同时从clock结构图可以看到进入A和D的clock在选择器之后没与其他模块有交集,因而,我们只需要把A和D的clock尽可能将做短即可。

我们也可以把一切交给EDA辅助工具,但这样的做的结果不能保证得到我们想要的结果。最好的办法是把进入到A、D两个Block的clock选择器以及其他clock分频逻辑固定在这两个block附近(下图中紫色区域),这样不仅能使clock line尽可能将以最短的距离抵达Block,同时也能尽可能将地增加common path的长度。

接下去考虑Block B/C和Macro/Macro2。鉴于他们之间的排程关系,我们期望它们之间的skew尽可能将短,同时common path要尽可能将长。在floorplan上我们可以看到它们被摆放成对称 的形式,因而,最简单直接的办法就是将所有与这几个block相关的逻辑都固定在两个Macro上方的正中间(假设其clock port在黄色标识的部分),如下图红色方框所示:

preplace区域示意到目前位置我们确定了须要preplace的逻辑以及其放置区域,接下去我们须要考虑如何实现我们的设想。其中首要的任务就是定义CTS的sdc。

对CTS辅助工具来说,要进行计时器树综合性,有一个必备的前提条件就是clock的定义,而后端斯特默是可以根据自己的策略自己调整clock的定义的。让我们再回忆以下clock的结构图:

特别针对上述结构,有两种常用的定义clock的方法(时间单位ps):

直接从所有的clock源头定义,此方法基本可以从func/test的sdc中直接复制clock的定义:create_clock -period 833.33 -name PLL1_CLK [get_pins PLL1/CLK] ;# 1.2GHz

create_clock -period 833.33 -name PLL2_CLK [get_pins PLL2/CLK] ;# 1.2GHz

create_clock -period 2000.00 -name FCLK1 [get_ports FCLK1] ;# 500MHz

create_clock -period 2000.00 -name FCLK2 [get_ports FCLK2] ;# 500MHz

create_clock -period 20000.00 -name TCLK1 [get_ports TCLK1] ;# 50MHz

create_clock -period 20000.00 -name TCLK2 [get_ports TCLK2] ;# 50MHz

2. 采用分段CTS的方法。因为大部分clock结构,从选择器开始都非常简单,因而我们可以从选择器的输出端定义一系列的clock并对有排程关系的部分进行balance;之后再从各个clock源头定义并在计时器树综合性的时候在选择器的输入停止。此方法的clock定义可以大体分为以下两部分:

第1段:选择器->各个Block

create_clock -period 833.33 -name MUXCLK1 [get_pins MUX1/Y]

create_clock -period 833.33 -name MUXCLK2 [get_pins MUX2/Y]

……

第2段:clock sources ->各个选择器

create_clock -period 833.33 -name PLL1_CLK [get_pins PLL1/CLK] ;# 1.2GHzcreate_clock -period 833.33 -name PLL2_CLK [get_pins PLL2/CLK] ;# 1.2GHz

create_clock -period 2000 -name FCLK1 [get_ports FCLK1] ;# 500MHz

create_clock -period 2000 -name FCLK2 [get_ports FCLK2] ;# 500MHz

create_clock -period 20000.00 -name TCLK1 [get_ports TCLK1] ;# 50MHz

create_clock -period 20000.00 -name TCLK2 [get_ports TCLK2] ;# 50MHz

至于如何使辅助工具在选择器停止,我们将在接下去的该文中继续讨论。同时我们将会把上述路子和策略通过真实

另外,在本文中涉及的design通过上述几幅图可以了解到相对详细的计时器结构,但在前述设计中我们如何事先得知clock的结构和排程关系呢?一般来说对业务流程完善的大公司,绘制详尽的计时器结构是前端斯特默的组织工作之一。但在前述工程项目中,面对的大部分design的clock结构图可能将是十分简单甚至完全没的情况,这时就须要后端技师多许多耐心去分析design,并积极与前端和constraint斯特默沟通,从而实现对design的计时器结构快速把握。

至此,CTS的策略基本构建完成。在接下去的该文中,我们将继续详细讨论那些策略的实现方法以及如何查看和debug clock的结果。

喜欢的话不要忘了点赞~

重磅消息:小编亲自参与制作的位数后端ICC2实践课程上线网易云课堂啦!

本课程【位数IC后端设计ICC2完全实践】主要以前述操作的形式用Synopsys后端辅助工具带我们从零开始完成一个后端设计小模块,包含后端实现、排程检查和物理验证等核心关键步骤的基础操作,以原生命令开始从头搭建业务流程完成设计,防止跑业务流程点按钮而得不到提高的问题,重点提高动手能力!现在可通过以下链接购买,加小编微信chen2mao2574还可领取大额优惠券,成功邀请同伴还可再享额外200元/人优惠,数量有限先到先得!

知乎时评: 【位数IC后端设计技师修炼之路】

时评其他该文:

【阎浮提】位数后端基础专业技能之:Clock Tree Synthesis(CTS)下篇

【阎浮提】位数后端基础专业技能之:Clock Tree Synthesis(CTS)中篇

【阎浮提】位数后端基础专业技能之:Clock Tree Synthesis(CTS)上篇

【阎浮提】位数后端基本专业技能之:绕线Congestion怎么解?

【阎浮提】后端Timing基础概念之:为何ICG容易出现setup violation?

【阎浮提】后端Timing基础概念之:为什么排程电路要满足setup和hold?

【阎浮提】后端Timing基本专业技能之:Hold Violation怎么修?

【阎浮提】后端Timing基本专业技能之:Setup Violation怎么修?