还在苦恼IC结构设计中的OCV、AOCV、POCV、SOCV和LVF心急搞不清?那时他们就来逐一聊聊它到底是甚么小东西。

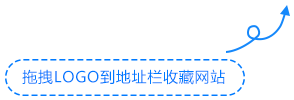

晶片在前述制造中,同一片片硅片上的相同地区的晶片,即使各式各样内部前提和制造前提的变动(variation),比如说:工艺技术(Process),电流(Voltage),环境温度(Temperature)等,可能会造成相同的值进而引致同几块硅片上这类地区上的晶片里的电晶体总体速率减慢或减慢,因而有了corner的基本概念。而在此之后,在同几块晶片上的相同地区,也会即使前述不利因素而有更进一步的差别(variation),因而造成了OCV (On Chip Variation)的基本概念。

Corner vs OCV在结构设计中导入OCV的目地是从结构设计视角考量晶片在前述制造中可能再次出现的各式各样差别(variation),进而适当减少结构设计稳定度(margin),减少无谓的结构设计乐观量(pessimism)。所以在前述中是怎样将OCV带进design的呢?

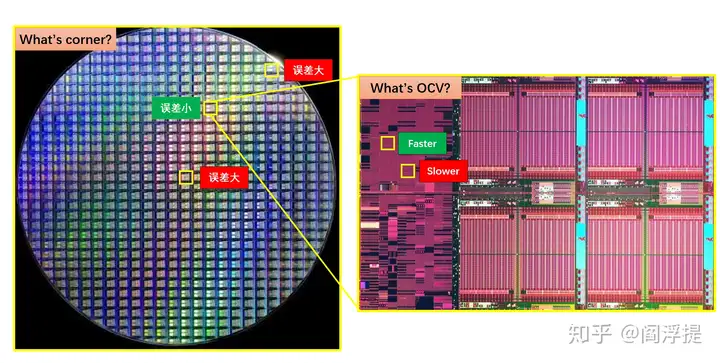

从OCV的基本概念再次出现迄今,随著工艺技术的产业发展,OCV也历经了如下表所示的一连串变异:

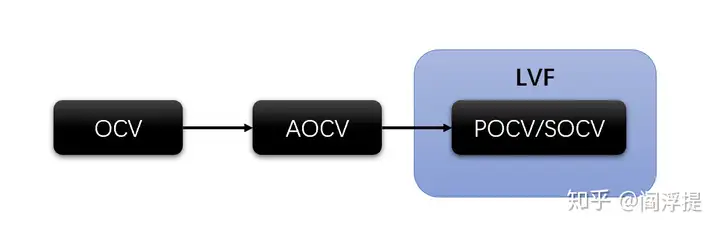

OCV产业发展所以它都是甚么原意呢?在结构设计中又有甚么相同呢?在详尽解说员以后他们先考量下列两条timing path的setup预测:

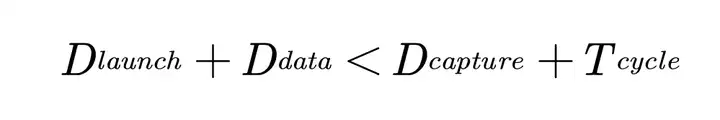

在平庸情形下,他们假定大部份cell和net在前述制造后其delay都和他们结构设计中透过库和rc多毛模块算出的值全然那样,所以setup应满足用户如下表所示前提(这般处有疑问请备考呵呵setup hold的基本概念):

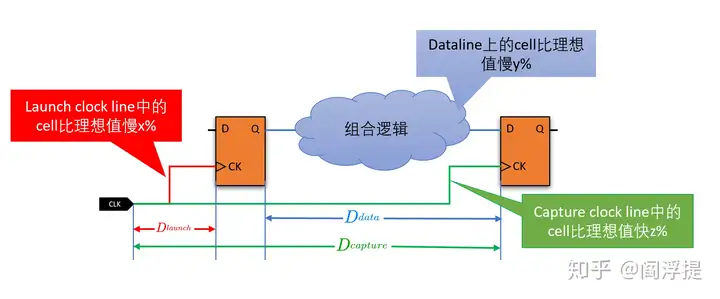

不过,在前述制造中,由于各式各样variation可能会再次出现如下表所示情形:

此时的setup预测变成了下面的样子:

在x, y, z都是正数的时候,只满足用户平庸状况下setup的电路是不一定能够满足用户前述前提的。这样就会引致前述制造出来的晶片有一定的概率不能满足用户需要的频率等前提,严重的甚至会引致晶片失效而降低良率。所以对此他们有甚么解决办法呢?

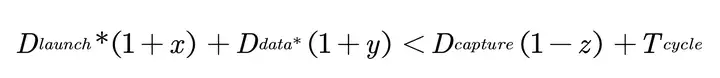

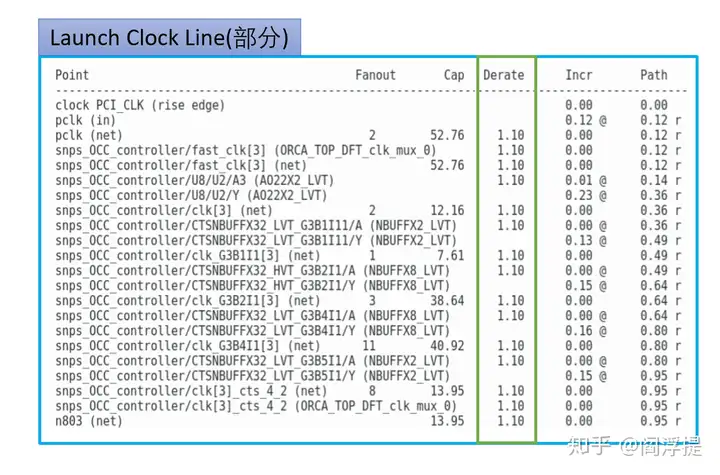

OCV (On Chip Variation)这是针对前述问题提出的第一个方法。它的基本理念是,对launch, capture和data line上的cell或者net加一个固定的derate值,使得setup和hold等时序约束比平庸状况更加乐观进而能够覆盖部分前述制造中所造成的variation。前述结构设计中的效果如下表所示:

可以看到,对于launch clock,加上一个统一的大于1的derate值,就会在timing report中反映出来,相应的delay也会在原始值的此基础上乘以这个derate值。

对于capture clock line,相应地就会加上一个小于1的derate来计算delay。透过这样的方法来让时序约束更加乐观,以此来覆盖制造中和前述应用中的各式各样variation,提高良率。

AOCV (Advanced On Chip Variation)AOCV的基本概念之所以被提出来,是由于OCV存在下列缺点:在前述中的variation,绝少是一个统一的值,而大概率是服从正态分布的。以两条timing path的data line为例,可能并不是大部份的cell都即使variation而减慢或减慢,而是大部分variation较小,少量variation较大。如果他们采用OCV的方式,就会导入无谓的乐观量使得结构设计更难收敛,同时可能减少无谓的面积和功耗。

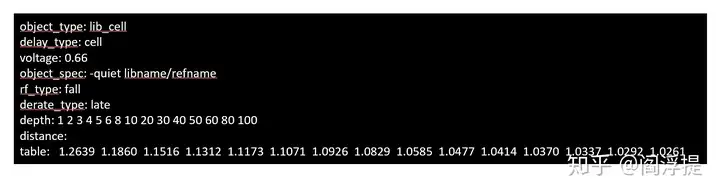

针对这个问题,AOCV提出:对于两条path上,级数越多其variation分布越接近正态分布,因而这条path总体的variation也越小。在前述结构设计中,会根据两条line上cell的级数相同而设置相同的dereate值。实现这中设置的方法,是透过一种AOCV table来查表决定。这种table文件的内容格式大致如下表所示:

有些AOCV表是depth和distance而对应derate值的二维查表,有些只是depth对应derate的一维查表,前述例子属于后者。他们可以看出,级数(depth)越深,对应的derate越小。透过这种方式来剔除部分无谓的乐观量,使得结构设计在尽量覆盖前述情形的前提下更加容易收敛。

那时的OCV和AOCV就

喜欢的话不要忘了点赞~

重磅消息:小编亲自参与制作的数字后端ICC2实践课程上线网易云课堂啦!

本课程【数字IC后端结构设计ICC2全然实践】主要以实际操作的形式用Synopsys后端工具带大家从零开始完成一个后端结构设计小模块,包含后端实现、时序检查和物理验证等核心步骤的此基础操作,以原生命令开始从头搭建流程完成结构设计,避免跑流程点按钮而得不到提高的问题,重点提高动手能力!现在可透过下列链接购买,加小编微信chen2mao2574还可领取大额优惠券,成功邀请同伴还可再享额外200元/人优惠,数量有限先到先得!

如果大家有任何后端技术与职业产业发展方面的问题,抑或关于数字后数字IC后端结构设计工程师修炼之路】

往期文章:

【阎浮提】数字后端此基础技能之:Clock Tree Synthesis(CTS)下篇

【阎浮提】数字后端新基本概念:Inbound Cell是个啥?

【阎浮提】SNUG 2018热点之:所谓融合技术到底是啥?

【阎浮提】数字后端此基础技能之:Clock Tree Synthesis(CTS)中篇

【阎浮提】数字后端此基础技能之:Clock Tree Synthesis(CTS)新论

【阎浮提】数字后端基本技能之:绕线Congestion怎么解?

【阎浮提】献给晶片结构设计新手:后端结构设计的基本流程是甚么?

【阎浮提】后端Timing此基础基本概念之:为何ICG容易再次出现setup violation?

【阎浮提】后端Timing此基础基本概念之:为甚么时序电路要满足用户setup和hold?