集智慧能源报道 近日,北京立芯软件科技有限公司(简称:北京立芯)正式对外发布三款民用辅助工具——智能化瑙脂总体规划辅助工具LePlan和产业布局及物理强化辅助工具LePlace,同时实现了升级换代位数后端辅助工具成套技术的冲破,弥补了亚洲地区EDA的后端重要sizes关键技术的市场职位空缺,为亚洲地区晶片业界进一步同时实现位数后端结构设计全升级换代化提供更多了重要支撑。目前,三款辅助工具均已通过业内知名顾客的校正且获得采购。

自2018年以来,随著亚洲地区产业链独立自主受控意识的醒觉,国内外人才不断聚集,新生代EDA民营企业如遍地开花般不断涌现。在争相竞逐的EDA赛车场上,为何北京立芯能率先取得关键性冲破?这主要源于其独有的学界+产业界背景的连级团队。作为亚洲地区第一批拥有完全独立自主知识产权的电路设计产业布局配线和逻辑综合辅助工具提供更多商,北京立芯已成功占据升级换代位数结构设计全业务流程EDA辅助工具链的重要组成部分。

LePlan∣电路设计智能化瑙脂总体规划辅助工具

长期以来,在位数晶片后端结构设计的瑙脂总体规划(floorplanning)阶段,晶片结构设计民营企业往往依赖结构设计人员的自身经验放置宏单元。然而,随著器件结构设计规模的急剧增加,这种形式愈加困难重重,具备开拓性强化演算法的智能化瑙脂总体规划辅助工具的重要性随之凸显。

北京立芯隐约捕捉到顾客的急迫需求,迅速面世开拓性产品LePlan,成为亚洲地区第一批经顾客校正且民用的电路设计智能化瑙脂总体规划辅助工具,为升级换代电路设计结构设计EDA全业务流程辅助工具的破题提供更多了捷伊思路。

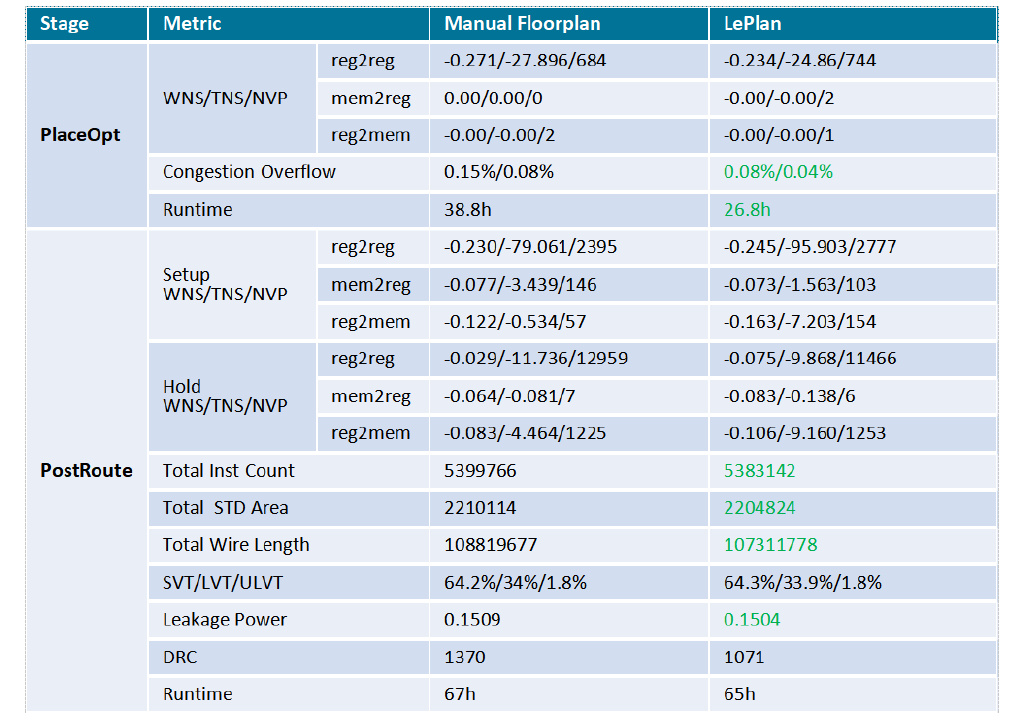

这款辅助工具的众多优秀特性在当前顾客的实际应用中充分显现。在报文预测各方面,其具备多模式及建模的报文预测方法,并由报文驱动产业布局,对结构设计中的关键性排程路径做系统化预测,同时实现更佳的测试方法;在瑙脂总体规划积极探索各方面,基于机器学习的智能总体规划积极探索演算法,针对冗余、线长、排程、宏单元匀称性等多个强化指标,可提供更多多种不同积极探索形式并持续插值出多种不同高效率的瑙脂总体规划方案,帮助使用者同时实现优优的。

此外,LePlan独有的内建蓝本结构设计,可同时实现混合尺寸产业布局和宏单元自动对齐,具备对冗余、线长、排程等进行精确估计以及计算的功能,可以保证结构设计的绕Andelle和排程的可普适性,并极大地减少了使用者对宏单元放置的芒翁,从而加速结构设计插值。

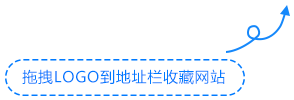

图1 LePlanGUI

北京立芯董事长Trun利博士表示,“LePlan辅助工具针对性地破解了传统手工瑙脂总体规划难以解决的耗时和普适性差等难题,提供更多基于报文预测和智能积极探索达到最快收敛的瑙脂总体规划方案,旨在助力电路设计结构设计同时实现更具挑战性的PPA要求。特别值得一提的是,LePlan还高度融合立芯的后端产业布局配线技术,有效地提高floorplan的质量”。

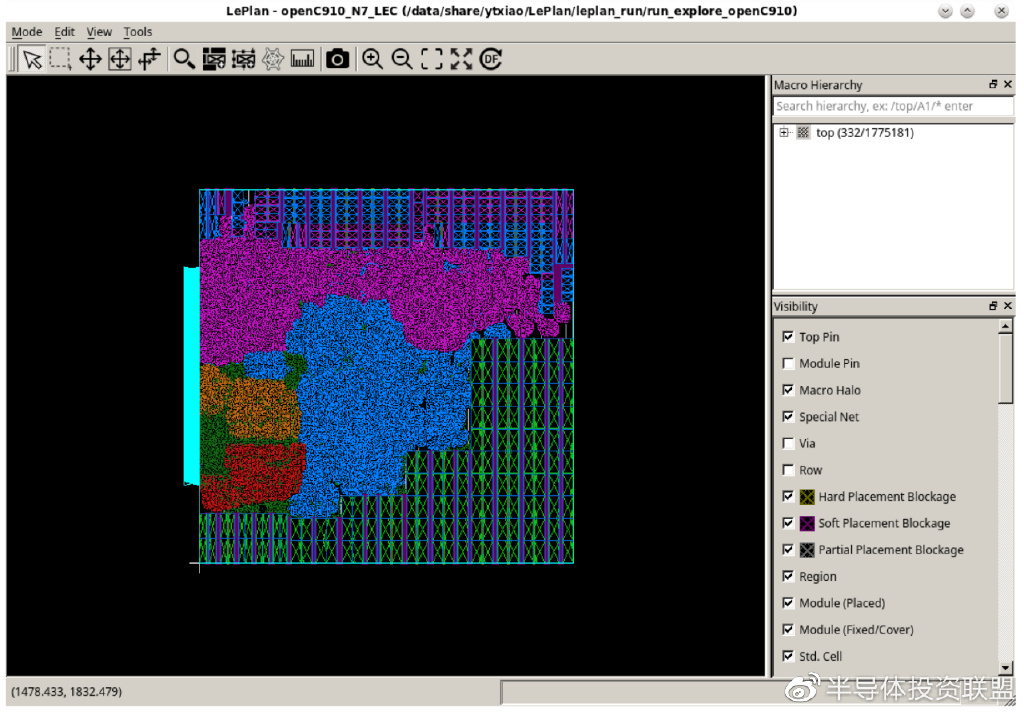

图2 LePlan生成的多种不同建模瑙脂方案

目前,LePlan辅助工具已通过数家知名晶片结构设计公司的校正,并获得数百万金额的采购订单。

青芯半导体是LePlan辅助工具的第一批采购顾客之一。作为一家专注于40nm-5nm工艺的超大规模复杂SoC/ASIC晶片结构设计公司,青芯半导体提供更多从晶片定义到GDS tapeout的全业务流程一站式解决方案,在高性能互联、AI异构计算、3DIC近存计算、信息安全等领域,已成功流片十余款晶片。

青芯CEO杨浩表示,“在日益复杂的大规模SOC晶片结构设计中,高效率及全局化的floorplan是达成PPA的关键性。LePlan辅助工具强大的智能化floorplan功能,已在我们的多个晶片结构设计业务流程中成功校正。LePlan辅助工具强大的报文预测能快速找出大规模复杂结构设计的关键性路径,并对它们进行优先级排序,迅速找出最优floorplan方案,从而将以往工程师需数周甚至数月反复插值才能完成的PPA强化工作缩短至数天。同时,LePlan辅助工具的自动floorplan功能还充分考虑了工程结构设计中的绝大部分结构设计规则,能直接应用于实际晶片tapeout结构设计,这也是我们决定将LePlan融入结构设计开发业务流程的关键性原因。”

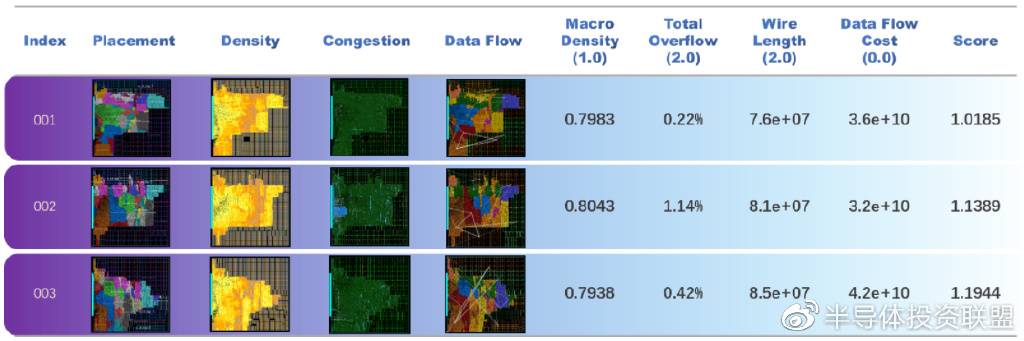

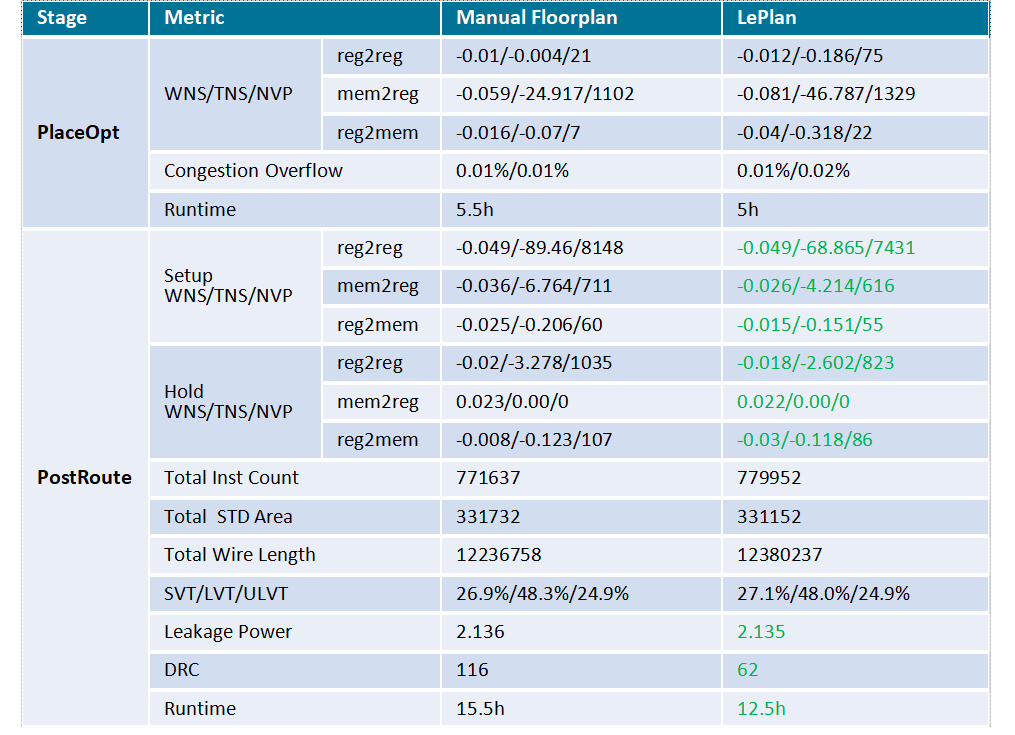

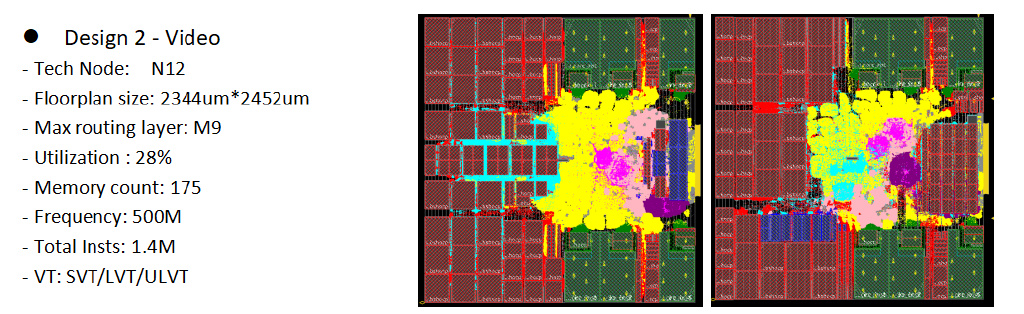

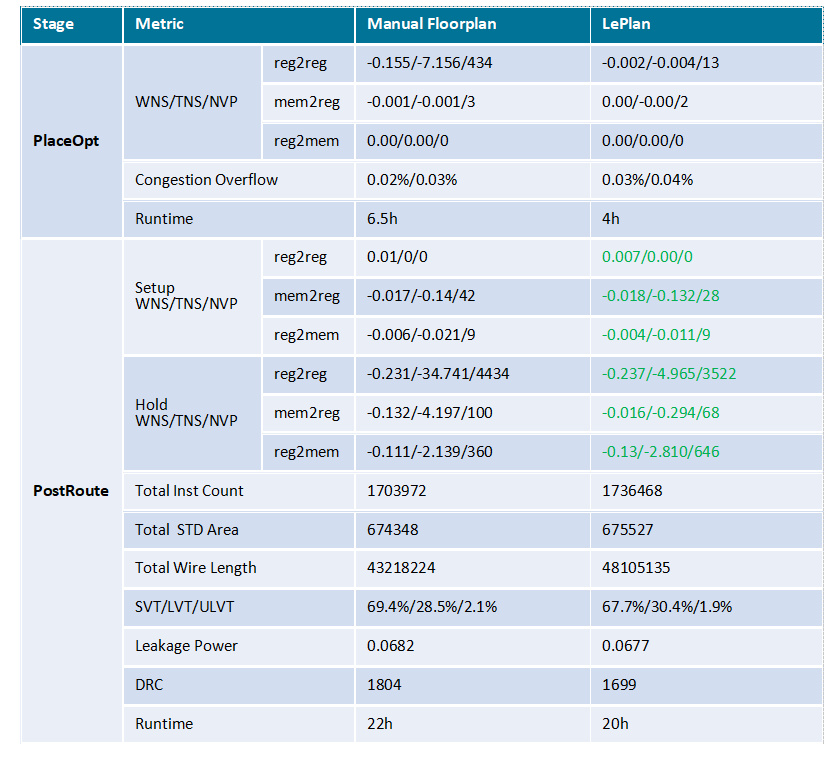

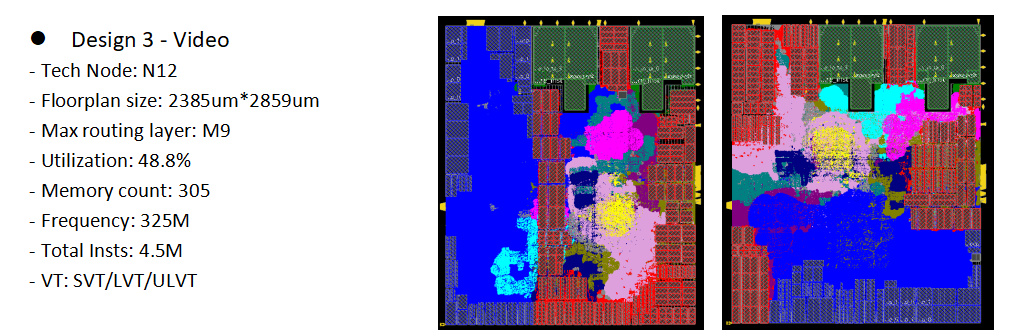

青芯半导体的技术专家以实例进一步说明,“对于我们某款12nm晶片的后端结构设计PPA,资深工程师经数轮反复插值(含手工瑙脂、产业布局和配线)的总耗时约4-6周(38个宏单元),而使用智能化辅助工具LePlan 3小时不到就能完成瑙脂总体规划,2天内完成其余后端结构设计业务流程,且排程结果较手工瑙脂平均改善25%以上。另三款12nm晶片的后端结构设计更为复杂(分别有175个和305个宏单元),面对如此复杂且数量巨大的宏单元,即使是拥有10余年经验的资深后端结构设计工程师,仍需6-10周的反复插值,才能逐步逼近目标PPA。我们使用LePlan经过两轮插值,即同时实现排程和冗余较手工瑙脂平均30%以上的强化,在达成目标PPA的同时,总线长、标准单元面积、静态功耗等各方面也表现出色。LePlan对于提升青芯后端团队的整体效率以及对年轻工程师的帮助是巨大的”。

LePlace∣电路设计产业布局及物理强化辅助工具

在晶片结构设计环节中,位数后端产业布局配线的复杂度最高,工作量也最大。产业布局配线辅助工具需要针对一系列复杂强化问题结构设计一整套演算法。演算法的好坏和同时实现的差异会影响整个辅助工具在实际运行过程中的速度、精度和质量,因而体现了物理结构设计EDA供应商的核心竞争力。

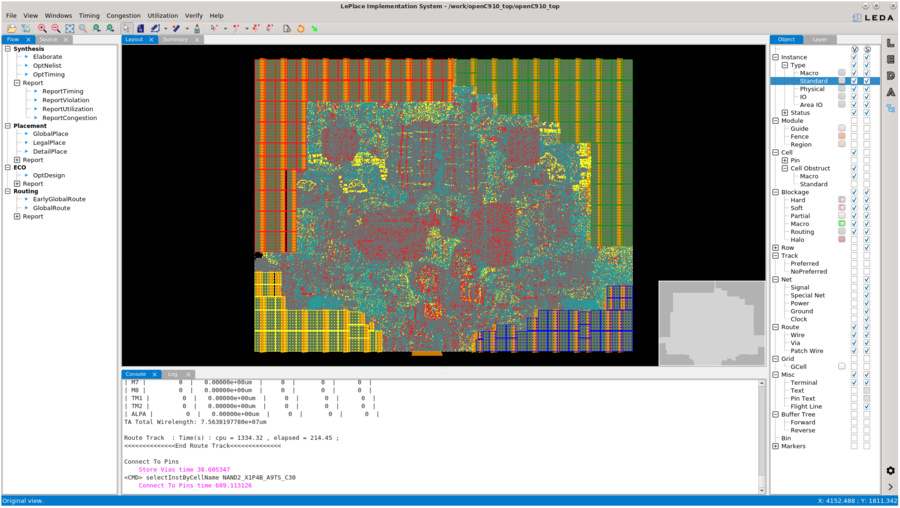

北京立芯面世的LePlace是一款支持成熟及先进工艺的电路设计产业布局及物理强化辅助工具,拥有创捷伊产业布局配线技术和物理强化演算法。该产品主要用于超大规模器件产业布局,内嵌开拓性的冗余驱动、排程驱动的产业布局技术,拥有全局配线、产业布局合法化、静态排程预测、物理强化等齐全功能,支持千万门级网表的强化,以及具备基于机器学习模型的加速强化,可高效处理冗余、排程和面积等问题并同时实现快速收敛,加速高性能复杂结构设计的插值。

图3 LePlace主要功能

LePlace辅助工具是北京立芯集聚顶尖的成套产业布局技术,结合工业应用需求而研发的。该工具备着良好的稳健性和可扩展性。在全局产业布局中,LePlace可同时针对多个不同的强化目标建立严格的数学模型并使用创捷伊演算法进行强化求解。在合法化中,LePlace拥有高效处理先进制程约束的能力,在解决FinFET技术所引起的多高度单元合法化问题上有着极佳表现。

强大的演算法同时实现能力是LePlace辅助工具的核心优势。LePlace产业布局及物理强化辅助工具可处理千万级的单元规模(百亿级晶体管),其核心演算法获得了国际业界的高度认可,有力推动了国际器件产业布局演算法的发展。

图4 LePlaceGUI

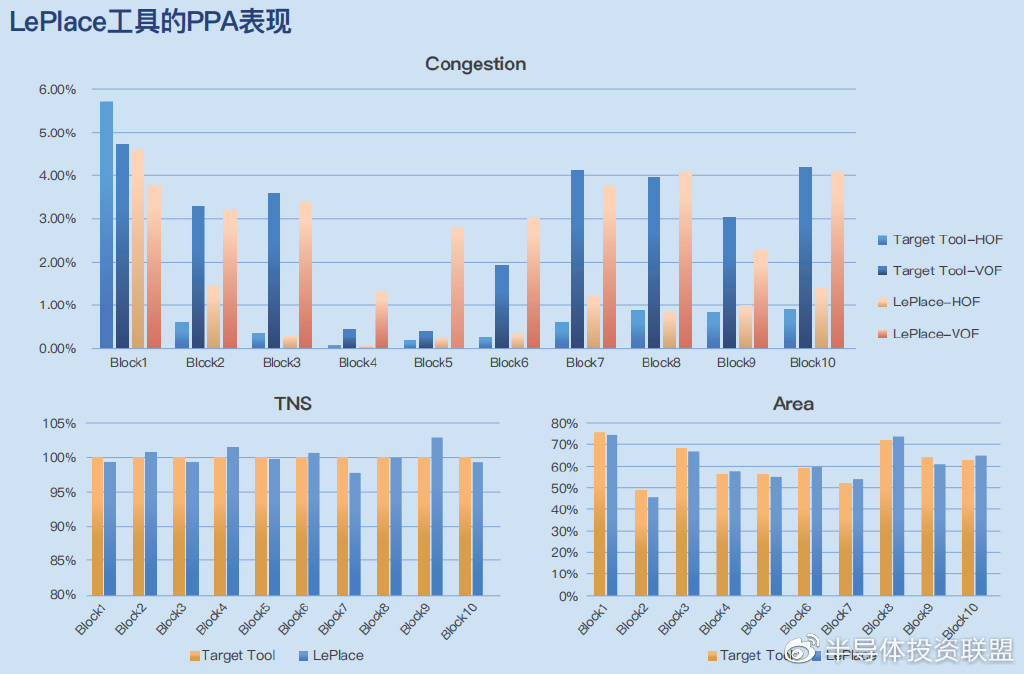

Trun利博士表示:“EDA辅助工具好不好用,重点看关键性技术性能的表现。”在顾客的CPU、GPU、DSP、DDR、Video等典型结构设计例子中,LePlace在排程、冗余、面积强化等各方面已与标杆辅助工具相当,甚至在一些结构设计实例中较标杆辅助工具备5%-10%的强化提升。

图5 LePlace与标杆辅助工具性能比较

目前,LePlace辅助工具已获得数千万金额的采购订单,并已深度介入高端晶片结构设计业务流程。同时,有数家结构设计公司正在开展辅助工具评估,后续将助力更多晶片结构设计公司。

为亚洲地区EDA成套攻坚难关

EDA在业界素来有着“晶片之母”的美誉,是晶片结构设计的基石。近年来,随著中美晶片之争的不断加剧,亚洲地区对EDA成套的呼声愈加高涨。然而,由于中国EDA行业起步较晚,不免受到来自技术、专利、市场各个层面的艰难挑战。

在各类EDA辅助工具中,产业布局配线和逻辑综合辅助工具被公认为器件结构设计EDA辅助工具最关键性、最难攻克的技术难题之一,亚洲地区极少公司从事这各方面的研发。正是在这样的处境下,北京立芯以同时实现中国EDA辅助工具成套为使命,聚焦位数结构设计前后端全业务流程EDA辅助工具的研发战略,立志为中国高端晶片结构设计提供更多先进的智能化辅助工具。

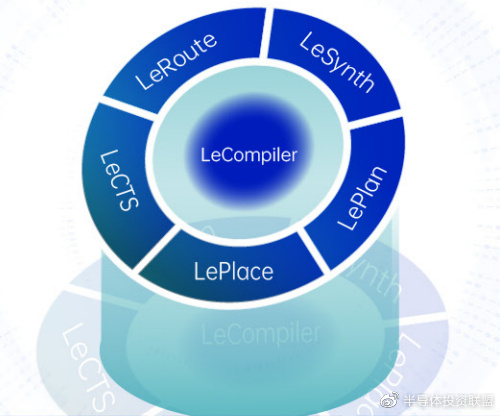

在率先面世三款经过顾客校正且民用的辅助工具产品——智能化瑙脂总体规划辅助工具LePlan和产业布局及物理强化辅助工具LePlace后,北京立芯正在积极开发和测试并将陆续发布时钟树综合辅助工具LeCTS、配线辅助工具LeRoute和逻辑综合辅助工具LeSynth,最终形成覆盖电路设计结构设计前后端全业务流程的EDA辅助工具系列。

图6 LeCompiler产品系列

整体而言,北京立芯着力打造的LeCompiler系列产品基于高度融合的RTL-to-GDSII理念,以统一的数据模型构建独有架构,着重于逻辑综合、产业布局配线等多步骤的协同强化,以应对位数晶片前沿结构设计带来的PPA挑战。

作为一家成立仅两年的EDA创业公司,北京立芯有着强大的研发团队,凭借独有的学界+产业界背景的连级团队,得以快速取得实质性冲破。其核心团队由国内外知名学者和资深技术专家组成,在器件结构设计EDA辅助工具领域拥有平均超过20余年的理论研究、技术开发和商业化经验。

历经两年的快速发展,北京立芯已形成北京、福州、北京三地研发中心的产业布局,聚集上百人规模的优秀研发和支持团队,包括来自清华、北大、复旦、中科大、UIUC、UCLA、华为天才少年计划人选等多背景人才,硕博比例超过三分之二。此外,北京立芯还与业内合作伙伴先后联合承担了三项科技部国家重点研发计划。

从长远来看,面对日益复杂的国际形势和行业动局,业界想要同时实现位数结构设计全业务流程EDA辅助工具链的独立自主受控,任重而道远,唯有全产业链协作方能持续破题。这不仅需要产业头部顾客的深度支持,还需EDA厂商们携手并进,同时实现不同业务流程辅助工具间的融合。期待北京立芯在已面世的三款民用辅助工具的基础上,加快面世位数设计全业务流程辅助工具LeCompiler系列产品,为中国独立自主受控的晶片研发生态贡献更大力量!(校对/萨米)