PDP的表述

如何认知PDP?我们做的什么样组织工作能认知为PDP的组织工作?

PDP即PDP掌控系统,IEEE(美国电机和电子零件技师联合会)对其表述是用作掌控、监控或者远距操作方式电脑和电子零件设备的器,是一种专供的计算机掌控系统;

国内两极化尊重的PDP掌控系统表述是以应用领域为中心,以电子零件计算机为依据,软硬体可上色,适应环境应用领域掌控网络系统机能、安全性、生产成本、表面积、耗电等严格把关的专供计算机掌控系统;

从应用领域第一类上予以表述来说,PDP掌控系统是应用软件和硬体的生态型,还能囊括机械设备等独立设置器。PDP掌控系统作为器或电子零件设备的一小部分,它是一个KParts储存在ROM中的PDPCPU组织工作台。

实际上,所有暗含位数USB的电子零件设备,如手环、电风扇、录影机、汽车等,都采用PDP系统,有些PDP掌控系统还包涵操作方式掌控系统,但绝大多数PDP掌控系统都是由一般而言设计模式整个掌控方法论。

PDP掌控系统发展的4个期:

1)单面微型计算机(SCM)期,即电脑系统黄金时代:掌控系统机能由直译器实现。

而此黄金时代掌控系统硬体:电脑系统。应用软件:无操作方式掌控系统。

主要就特征:掌控普莱邦相对单个,处置组织工作效率低,储存空间十分非常有限,几乎无使用者

USB。

2)中央CPU(MUC)期,主要就技术路径:不断扩充第一类掌控系统要求的各式各样西向电阻

和USB电阻,凸显其第一类的智能掌控能力

而此期基础:PDP中央CPU。而此期核心理念:单纯操作方式掌控系统。

主要就特征:硬体采用PDP中央CPU,中央CPU的类型多样,适用性弱;掌控系统开支小,组织工作效率较低。

3)KMH掌控系统(SOC):主要就特征:PDP系统能够运转于各式各样不同的中央CPU上,

相容性好,操作方式掌控系统的内核小,效果好。

4)internet为标志的PDP掌控系统:PDP网络化主要就表现:一方面是PDP

CPU集成了网络USB

另一方面是PDP电子零件设备应用领域于网络环境中。

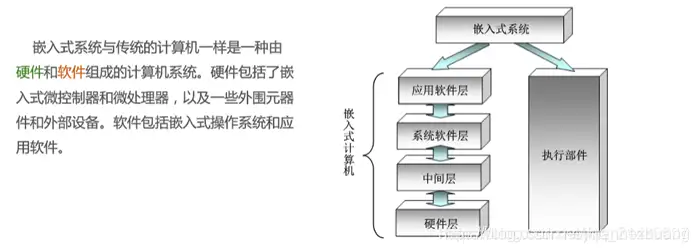

PDP掌控系统的组成

一、硬体层中包涵

1.PDP中央CPU

2.储存器(SDRAM、ROM、Flash等)

3.通用电子零件设备USB和I/OUSB(A/D、D/A、I/O等)

在一片PDPCPU基础上添加电源电阻、时钟电路和储存器电阻,就构成了一个PDP核心理念掌控模块。也就是我们所说的电脑系统,其中操作方式掌控系统和应用领域程序都能固化在ROM中。

(1)PDP中央CPU:硬体层的核心理念

PDP掌控系统硬体层的核心理念是PDP中央CPU,PDP微处理器与通用CPU最大的不同在于PDP中央CPU大多组织工作在为特定使用者群所专供设计的掌控系统中,它将通用CPU(例如51电脑系统)许多由板卡完成的任务集成在芯片内部,从而有利于PDP掌控系统在设计时趋于小型化,同时还具有很高的组织工作效率和安全性。这里能认知为STM32电脑系统和51电脑系统的不同。

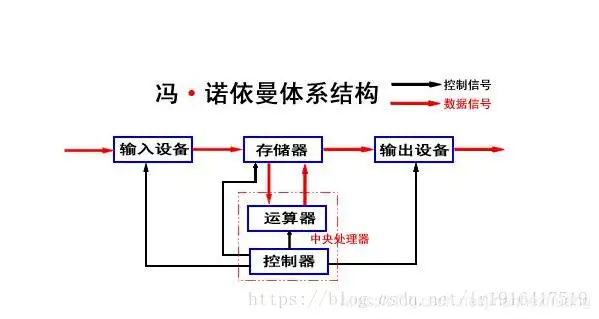

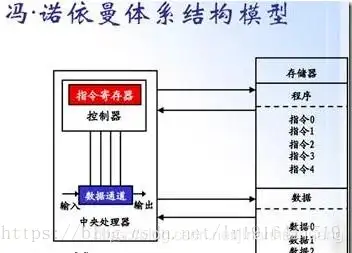

PDP中央CPU的体系结构能采用冯·诺依曼体系或哈佛体系结构;

1)冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令储存器和数据储存器 合并在一起 的储存器结构。取指令和取操作方式数都在同一总线上,通过分时复用的方式进行;

缺点是在高速运转时,不能达到同时取指令和取操作方式数,从而形成了传输过程的瓶颈。由于程序指令储存地址和数据储存地址指向同一个储存器的不同物理位置,因此程序指令和数据的宽度相同,如英特尔公司的8086中央CPU的程序指令和数据都是16位宽。

指令掌控系统能选用精简指令掌控系统(Reduced Instruction Set Computer,RISC)和复杂指令掌控系统CISC(Complex Instruction Set Computer,CISC)。

RISC计算机在通道中只包涵最有用的指令,确保数据通道快速执行每一条指令,从而提高了执行组织工作效率并使CPU硬体结构设计变得更为单纯。PDP中央CPU有各式各样不同的体系,即使在同一体系中也可能具有不同的时钟频率和数据总线宽度,或集成了不同的外设和USB。

据不完全统计,全世界嵌入式中央CPU已经超过1000多种,**体系结构有30多个系列,其中主流的体系有ARM、MIPS、PowerPC、X86和SH等。**但与全球PC市场不同的是,没有一种PDP中央CPU能主导市场,仅以32位的产品而言,就有100种以上的PDP中央CPU。PDP中央CPU的选择是根据具体的应用领域而决定的。

(2)储存器:PDP掌控系统需要储存器来存放和执行代码。

PDP掌控系统的储存器包涵Cache、主存和远距储存器。

1、Cache

Cache是一种容量小、速度快的储存器阵列它位于主存和PDP中央CPU内核之间,存放的是一段时间中央CPU采用最多的程序代码和数据。

在需要进行数据读取操作方式时,中央CPU尽可能的从Cache中读取数据,而不是从主存中读取,这样就大大改善了掌控系统的性能,提高了中央CPU和主存之间的数据传输速率。

Cache的主要就目标就是:减小储存器(如主存和远距储存器)给中央CPU内核造成的储存器访问瓶颈,使处置速度更快,实时性更强。

在PDP掌控系统中Cache全部集成在PDP中央CPU内,可分为数据Cache、指令Cache或混合Cache,Cache的大小依不同CPU而定。一般中高档的PDP中央CPU才会把Cache集成进去。

2、主存

主存是PDP中央CPU能直接访问的寄存器,用来存放掌控系统和使用者的程序及数据。它能位于中央CPU的内部或外部,其容量为256KB~1GB,根据具体的应用领域而定,一般片内储存器容量小,速度快,片外储存器容量大。

常用作主存的储存器有:ROM类:NOR Flash、EPROM和PROM等。RAM类:SRAM、DRAM和SDRAM等。其中NOR Flash 凭借其可擦写次数多、储存速度快、储存容量大、价格便宜等优点,在PDP领域内得到了广泛应用领域。

3、远距储存器

远距储存器用来存放大数据量的程序代码或信息,它的容量大、但读取速度与主存相比就慢的很多,用来长期保存使用者的信息。PDP掌控系统中常用的外存有:硬盘、NAND Flash、CF卡、MMC和SD卡等。

(3)通用电子零件设备USB和I/OUSB

PDP掌控系统和外界交互需要一定形式的通用电子零件设备USB,如A/D、D/A、I/O等,外设通过和片外其他电子零件设备的或传感器的连接来实现中央CPU的输入/输出机能。

每个外设通常都只有单个的机能,它能在芯片外也能内置芯片中。

PDP掌控系统中常用的通用电子零件设备USB有A/D(模/数转换USB)、D/A(数/模转换USB),I/OUSB有RS-232USB(串行通信USB)、Ethernet(以太网USB)、USB(通用串行总线USB)、音频USB、VGA视频输出USB、I2C(现场总线)、SPI(串行西向电子零件设备USB)和IrDA(红外线USB)等。

二、中间层:

硬体层与应用软件层之间为中间层,也称为硬体抽象层(Hardware Abstract Layer,HAL)或板级支持包(Board Support Package,BSP),它将掌控系统上层应用软件与底层硬体分离开来,使掌控系统的底层驱动程序与硬体无关,上层应用软件开发人员无需关心底层硬体的具体情况,根据BSP 层提供的USB即可进行开发。

该层一般包涵相关底层硬体的初始化、数据的输入/输出操作方式和硬体电子零件设备的配置机能。

BSP具有以下两个特征:

1.硬体相关性:因为PDP实时掌控系统的硬体环境具有应用领域相关性,而作为上层软 件与硬体平台之间的USB,BSP需要为操作方式掌控系统提供操作方式和掌控具体硬体的方法。

2.操作方式掌控系统相关性:不同的操作方式掌控系统具有各自的应用软件层次结构,因此,不同的操作方式掌控系统具有特定的硬体USB形式。

实际上,BSP是一个介于操作方式掌控系统和底层硬体之间的应用软件层次,包括了掌控系统中大部分与硬体联系紧密的应用软件模块。

设计一个完整的BSP需要完成两部分组织工作:PDP掌控系统的硬体初始化以及BSP机能,设计硬体相关的电子零件设备驱动。

三、掌控系统应用软件层:

由实时多任务操作方式掌控系统(Real-timeOperation System , RTOS)、文件掌控系统、图形使用者界面USB(Graphic User Interface , GUI)、网络掌控系统及通用组件模块组成

————————————————

版权声明:本文为CSDN博主「贺赫赫813」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/jinanhezhuang/article/details/109838718

如有侵权,请联系删除。